MIL-EMBEDDED.COM

# EMBEDDED SYSTEMS VOLUME 5 NUMBER 7 OCTOBER 2009

INCLUDING

#### Chris A. Ciufo

OpenVPX: Conflict to collaboration

#### Field Intelligence

Processing potential of GPUs

#### Mil Tech Insider

Prepping for lead-free

#### **Legacy Software Migration**

Micro Focus

Modernizing with static analysis

## Mil apps blend real-time with realism

#### Also:

Does EAL 6+ make the grade?

An interview with Wind River's Marc Brown

Supplement inside:

## Total-ACE™

Complete MIL-STD-1553

Single Package Solution

MIL-STD-1553 Terminal & Transformer Solution!

LESS ... SPACE!

LESS ... COMPLEXITY!

LESS ... COST!

www.ddc-web.com T

Toll Free: 1-800-DDC-5757

#### **Avionics Databus Test, Simulation & Embedded Solutions**

Lightweight, small, rugged, reliable, feature rich and cost-effective. These are only a few of the benefits of the new AB2000 series of Avionics BusBoxes® from Ballard Technology. They deliver outstanding avionics performance with multi-protocol and flexible expansion capabilities. Conductively cooled, the AB2000 is ideal for rugged avionics applications such as serving and recording data, converting protocols and providing federated control. Find out today how AB2000 innovation can work for you.

#### Innovation for your success

For more information call 425.339.0281 or visit us at www.ballardtech.com

## EMBEDDED SYSTEM

October 2009 Volume 5 Number 7

#### **COLUMNS**

#### Field Intelligence

Releasing the processing potential of GPUs

By Duncan Young

#### Mil Tech Insider

Preparing for lead-free electronics By John Wemekamp

#### **Legacy Software Migration**

Modernizing legacy military systems with top-grade static analysis

By Tom Schultz, Coverity

#### **Crosshairs Editorial**

OpenVPX goes from conflict to 54 collaboration

By Chris A. Ciufo

#### DEPARTMENTS

14-15 Daily Briefing: News Snippets

By Sharon Schnakenburg

52-53 Editor's Choice Products

#### ON THE COVER:

Simulated but realistic graphics environments are an essential part of military operations. They can be used for training purposes, honing operator skills without the risk of life or equipment loss. They're also how pilots operate Unmanned Aerial Systems (UASs) remotely, as drones replace manned aircraft. In this issue of *Military Embedded Systems*, Yannick Lefebvre of Presagis (page 23) describes ways to create simulated environments for UAS operator training. And our resident "gray beard" Duncan Young follows upon last month's Quantum3D article on mobile graphics technology with his own opinion on the subject of Graphics Processor Units or GPUs (page 8). [Cover photo: A B-1B Lancer flies a combat patrol over Afghanistan in support of Operation Enduring Freedom, while a civilian aircraft approach is mapped out virtually. B-1B photo courtesy of U.S. Air Force/Staff Sgt. Aaron Allmon; inset courtesy of Quantum3D]

ISSN: Print 1557-3222

All registered brands and trademarks within Military Embedded Systems magazine are the property of their respective owners.

© 2009 OpenSystems Media © 2009 Military Embedded Systems

#### Software: Making the grade - EAL 6+

16 'EAL 6+' says it all - or does it?

> Q&A with Marc Brown, Vice President, VxWorks Product Strategy and Marketing for Wind River Systems

#### Hardware: Mil apps blend real-time with realism

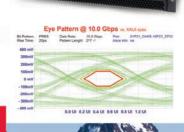

20 10 GbE in net-centric warfare: Why commercial network cards can't drive the application

By Rob Kraft, AdvancedIO Systems Inc.

Creating a simulated environment for **UAS operator training**

By Yannick Lefebvre, Presagis

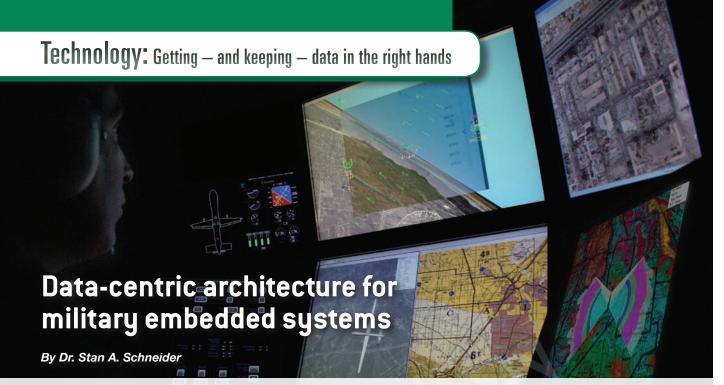

#### Technology: Getting – and keeping – data in the right hands

Data-centric architecture for military embedded systems

By Dr. Stan A. Schneider, Real-Time Innovations, Inc.

#### Special: Blade balances power and performance

CompactPCI solution targets rugged apps

By Jeff Munch, Ampro ADLINK Technology, Inc.

42 **Executive Speakouts**

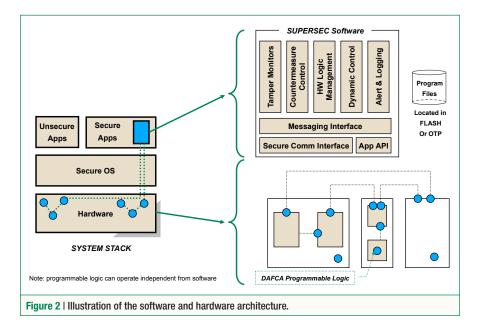

Protecting today's military electronics systems with real-time hardware/software protection countermeasures

By Paul Bradley, DAFCA, Inc.

#### Mil Tech Trends: VPX rising

48 Taking the VPX ecosystem to the next level

By Justin Moll, Elma Bustonic

#### **EVENTS**

www.opensystemsmedia.com/events

#### SAE AeroTech Congress & Exhibition

November 10-12, 2009 • Seattle, WA www.sae.org/events/conferences/aerospace/#2009

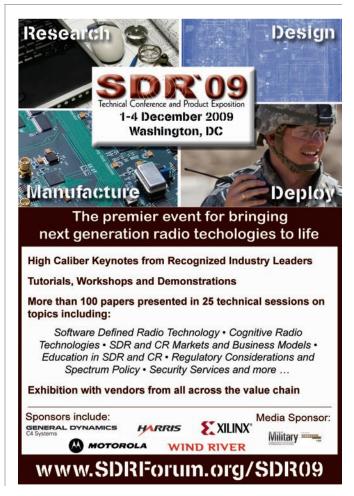

#### SDR'09 Technical Conference and Product Exposition

December 1-4, 2009 • Washington, DC www.sdrforum.org/SDR09

#### WEB RESOURCES

Subscribe to the magazine or E-letter Live industry news • Submit new products

http://submit.opensystemsmedia.com

#### White papers:

Read: http://whitepapers.opensystemsmedia.com Submit: http://submit.opensystemsmedia.com

## We Won't Leave You High and Dry.

Recent consolidations in the embedded industry have left many PowerPC® users wondering where their next real-time or embedded Linux® operating system will come from.

At LynuxWorks, we are here to help. Our new PowerPC rescue package offers an open-standards based RTOS or embedded Linux, and a migration kit to help PowerPC users stay with their processor of choice.

Visit www.lynuxworks.com/rescue-me to request a migration whitepaper and an emergency hand-crank flashlight-radio\*.

Open.Reliable.Safe.Secure.

#### ADVERTISER INFORMATION

| ADVE             | RIISER INFORMATION                                                             |

|------------------|--------------------------------------------------------------------------------|

| Page             | Advertiser/Ad title                                                            |

| 34 MCD           | ACT/Technico – Solid state storage solutions                                   |

| 51               | Alphi Technology Corporation – The expert in                                   |

|                  | Military Technologies                                                          |

| 7                | Annapolis Micro Systems, Inc. – WILDSTAR 5                                     |

| 30 MCD           | Annapolis Micro Systems, Inc. – WILDSTAR 5                                     |

| 3                | Ballard Technology – Innovation sets us apart                                  |

| 17               | Conec Corporation – CONEC Embedded Series                                      |

| 56               | Curtiss-Wright Controls Embedded Computing –                                   |

| 2                | Rugged deployed electronic systems  Data Device Corp. (DDC) – Total-ACE        |

| 38 MCD           | ELMA Electronic – Cutting edge backplanes                                      |

| 43 MCD           | ELMA Electronic – Cutaing eage backplaines  ELMA Electronic – Rethink MicroTCA |

| 12               | ELMA Electronic – VPX                                                          |

| 35 MCD           | Excalibur Systems, Inc. – Ready for                                            |

|                  | the unexpected?                                                                |

| 13               | Excalibur Systems, Inc. – Dense?                                               |

| 55               | GE Fanuc Intelligent Platforms, Inc. –                                         |

|                  | Which of these platforms use GE Fanuc                                          |

| 21               | Great River Technology, Inc. – ARINC 818                                       |

| 33 MCD           | Hartmann Elektronik – VME                                                      |

| 19               | Kontron – We do not build Navy ships                                           |

| 44 MCD<br>42 MCD | Kontron – We do not build Navy ships<br>LCR Electronics – Three rugged         |

| 42 IVIUD         | AdvancedTCA chassis                                                            |

| 5                | LynuxWorks, Inc. – We won't leave you                                          |

| ·                | high and dry.                                                                  |

| 42 MCD           | MEN Micro Elektronik GmbH – PICMG 2.30                                         |

|                  | CompactPCI PlusIO SBC                                                          |

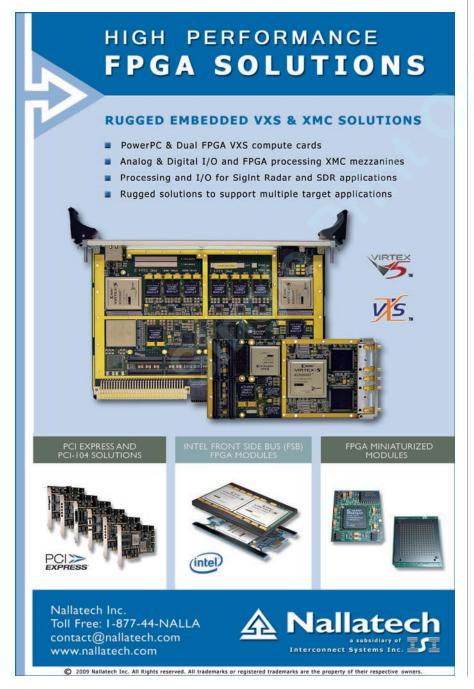

| 18               | Nallatech – High performance FPGA solutions                                    |

| 25               | Parvus Corporation – Qualified to perform                                      |

| 22               | Phoenix International – Data storage                                           |

| 31 MCD           | Positronic Industries – PICMG Power Connectors                                 |

| 37 MCD           | RadiSys Corporation – Next Generation<br>COTS-Based Solutions                  |

| 42 MCD           | RadiSys Corporation – Leveraging a ruggedized                                  |

| 1211100          | AdvancedTCA platform                                                           |

| 40 MCD           | Schroff a Brand of Pentair Electronic                                          |

|                  | Packaging – Performance                                                        |

| 33 MCD           | Schroff a Brand of Pentair Electronic                                          |

| 00 1400          | Packaging – XTCA Cube                                                          |

| 39 MCD           | Schroff a Brand of Pentair Electronic Packaging – Planning your next product?  |

| 53               | SDR Forum – SDR '09                                                            |

| 22               | TEWS Technologies LLC – COTS I/O Solutions                                     |

| 27               | Themis Computer – Themis has                                                   |

|                  | Speed to Burn                                                                  |

| 28               | Trident Space and Defense – Protect your data                                  |

| 24               | Tri-M Systems Inc. – 100Mhz PC/104 Module                                      |

| 47               | Tri-M Systems Inc. – PC/104 Can-Tainer                                         |

| 50               | VersaLogic Corp. – When you're at 30,000 feet,                                 |

|                  | quality matters                                                                |

| 49               | VPT Inc. – Efficent, reliable power                                            |

| 10               | White Electronic Designs – Trapped in your design?                             |

| 41 MCD           | your design:                                                                   |

#### **E-LETTER**

41 MCD

Nov/Dec: www.mil-embedded.com/eletter

Cell phones: The next great *software* driver By Chris A. Ciufo

XTech - The XTech Files

Pulling out secrets: New technologies help military find intelligence in degraded documents By Dr. Steven Schlosser, NovoDynamics

### Military EMBEDDED SYSTEMS

**DSP-FPGA.com**

PC/104 small form factors

Embedded COMPUTING

#### Military & Aerospace Group

Chris Ciufo, Group Editorial Director cciufo@opensystemsmedia.com

#### Sharon Schnakenburg

Assistant Managing Editor sschnakenburg@opensystemsmedia.com

Jennifer Hesse, Assistant Managing Editor jhesse@opensystemsmedia.com

Terri Thorson, Senior Editor (columns) tthorson@opensystemsmedia.com

Monique DeVoe, Copy Editor

Hermann Strass, European Representative hstrass@opensystemsmedia.com

Konrad Witte, Senior Web Developer

Steph Sweet, Creative Director

Joann Toth, Senior Designer

David Diomede, Art Director

#### Phyllis Thompson

Circulation/Office Manager subscriptions@opensystemsmedia.com

#### Sales Group

Dennis Doyle, Senior Account Manager ddoyle@opensystemsmedia.com

Tom Varcie, Senior Account Manager tvarcie@opensystemsmedia.com

Rebecca Barker, Strategic Account Manager rbarker@opensystemsmedia.com

#### Andrea Stabile

Advertising/Marketing Coordinator astabile@opensystemsmedia.com

Christine Long, Digital Content Manager clong@opensystemsmedia.com

#### **International Sales**

Dan Aronovic, Account Manager - Israel daronovic@opensystemsmedia.com

Sam Fan, Account Manager - Asia sfan@opensystemsmedia.com

#### **Regional Sales Managers**

Ernest Godsey, Central and Mountain States egodsey@opensystemsmedia.com

Barbara Quinlan, Midwest/Southwest bquinlan@opensystemsmedia.com

Denis Seger, Southern California dseger@opensystemsmedia.com

Sydele Starr, Northern California sstarr@opensystemsmedia.com

Ron Taylor, East Coast/Mid Atlantic rtaylor@opensystemsmedia.com

#### Reprints and PDFs

Nan Lamade 800-259-0470

republish@opensystemsmedia.com

#### **Editorial/Business Office**

16626 E. Avenue of the Fountains, Ste. 203 Fountain Hills, AZ 85268

Tel: 480-967-5581 Fax: 480-837-6466 Website: www.opensystemsmedia.com

Publishers: John Black, Michael Hopper, Wayne Kristoff

Vice President Editorial: Rosemary Kristoff

Vice President Marketing & Sales:

Patrick Hopper

phopper@opensystemsmedia.com

Business Manager: Karen Layman

## **Annapolis Micro Systems**The FPGA Systems Performance Leader

## WILDSTAR 5 for IBM Blade The Perfect Blend of Processors and FPGAs

Fully Integrated into IBM Blade Management System

Abundant Power and Cooling Ensure Maximum Performance

Made in the USA

#### **Ultimate Modularity**

From 2 to 8 Virtex 5 FPGA/Memory Modules Input / Output Modules Include: Quad 130 MSps thru Quad 500 MSps A/D 1.5 GSps thru 2.2 GSps, Quad 600 MSps A/D Dual 1.5 GSps thru 4.0 GSps D/A Infiniband, 10 G Ethernet, FC4, SFPDP

Direct Seamless Connections with no Data Reduction

Between External Sensors and FPGAs

Between FPGAs and Processors over IB or 10GE Backplane

Between FPGAs and Standard Output Modules

190 Admiral Cochrane Drive, Suite 130, Annapolis, Maryland USA 21401 wfinfo@annapmicro.com (410) 841-2514 www.annapmicro.com

#### Field Intelligence

#### Releasing the processing potential of GPUs

The internal computing architecture of high-performance Graphics Processing Units (GPUs) has evolved from fixedfunction graphics execution units to arrays of fully programmable Single Instruction Multiple Data (SIMD) processors. This evolution has been driven by the demand from the video gaming community to perform generic physics calculations in parallel to give greater realism to the behavior of, for example, smoke, debris, fire, and fluids. The ability to offload and accelerate these same types of repetitive parallel calculations onto a GPU offers great potential to military technologies such as radar, sonar, and image processing. The key to efficient implementation is a new generation of tools such as OpenCL and CUDA, which integrate code development across heterogeneous CPU/GPU architectures along with the memory and I/O bandwidth to support them.

#### SIMD processing rays

At its heart, a high-performance GPU device will typically have up to 128, 32-bit single precision processor cores clocked at 1 GHz or more. These are organized as parallel SIMD arrays so that groups of processors can execute the same instructions on different data sets in parallel. When operating as a GPU, the primary requirement is to utilize animated 3D graphics functions such as shaders. However, GPUs are evolving away from being specific shader processors and are becoming more generic math processors, now referred to as "stream processors." With the right tools, GPUs can be applied much more broadly to accelerate many kinds of PC-based applications such as genetic research, seismic processing, meteorological processing, and DSP, at much lower cost than other more specific forms of hardware acceleration.

One major GPU manufacturer, NVIDIA, has developed a software environment known as CUDA to release the potential of the GPU into these other application areas. CUDA supports the combination of CPU and GPU by allowing inline C code

development through an abstracted library of functions that hides the specifics of the GPU's stream processors and their interface with the CPU. This provides a very flexible programming interface and permits growth or even radical change of the stream processors in the future, without impacting existing code. To reduce the scope for errors, CUDA adopts a straightforward programming model that manages multiple threads internally to optimize processor utilization so that there is no need to write explicitly threaded code.

#### **GPU** without graphics

Paradoxically there will be a class of embedded applications that will not generate any local graphical output at all. Typically, this class could comprise image processing in UAVs or underwater Remotely Operated Vehicles (ROVs) or many other types of unmanned sensors. An embedded PC with GPU becomes an ideal platform for image enhancement, stabilization, pattern recognition, target tracking, video encoding, or encryption/ decryption. These are all applications that can be written in regular C code to run on a high-performance PC but could be accelerated to run orders of magnitude faster by a GPU stream processor. The GPU provides generic parallel processing already integrated into many PC configurations and requires less specialized skills than, for example, an FPGA development, by using offthe-shelf tools such as CUDA, the MathWorks' MATLAB, and ported VSIPL DSP libraries to construct, test, and verify the application.

#### PCI Express key to performance

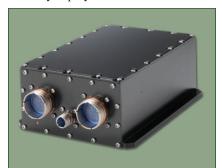

An embedded sensor processing application requires high data bandwidth to receive and process the continuous stream of incoming raw image data. The ability of CUDA to handle multithreading and consequently maximize the processing load of the GPU's SIMD arrays is dependent on the performance of both the external interface and its local memory interface. High-end GPU devices will

use 16-lane PCI Express 2.0, doubling the earlier PCI Express 1.0 data rates, to give a theoretical 500 MBps per lane. For rugged embedded applications, this fits well with both the popular 3U and 6U formats of the VPX (ANSI/VITA 46) packaging standards with their extended high-speed connectivity. The MAGIC1 rugged embedded PC from GE Fanuc Intelligent Platforms, pictured in Figure 1, is based on the 3U VPX form factor and has been reengineered and enhanced to support CUDA-capable GPUs from NVIDIA. While such an embedded PC fits comfortably within the 3U format, a 6U profile also has the real estate and greater connectivity to potentially make a new class of powerful multicomputing engine based on a number of multicore processors and GPUs using PCI Express 2.0 as the interconnect.

The GPU is evolving rapidly, creating a processing capability with broad application across many diverse markets. CUDA and similar development environments provide accessibility to this untapped performance reserve. Consequently, the rugged military and aerospace domain appears set to change the way complex, time-consuming sensor applications can be developed, tested, verified, and successfully deployed.

Figure 1 | MAGIC1 is a rugged, embedded PC from GE Fanuc Intelligent Platforms, based on the 3U VPX form factor and reengineered and enhanced to support CUDA-capable GPUs from NVIDIA.

To learn more, e-mail Duncan Young at young.duncan1@btinternet.com.

#### Mil Tech Insider

#### Preparing for lead-free electronics

By John Wemekamp

Commercial and domestic electronics products of all types have been heavily influenced by the European directives for Restriction of the use of certain Hazardous Substances (RoHS) and Waste Electrical and Electronic Equipment (WEEE). Across industry, the most significant change has been the rapid adoption of lead-free solder. The worldwide component supply chain is now fully geared up to provide lead-free terminations for all types of components as first choice, while some manufacturers are still offering traditional tin/lead as an alternative but at an increasingly higher cost. Military and aerospace equipment vendors, integrators, and end users are still apprehensive about using lead-free materials. This is because of lingering doubts about the critical long-term reliability of lead-free electronics in the more highly stressed temperature and mechanical environments of many military applications.

#### GEIA-STD-0005-1

As a result of the worldwide lead-free initiatives, future military contracts will require lead-free project plans. For the U.S. DoD, these will need to be in accordance with GEIA-STD-0005-1 "Performance Standard for Aerospace and High Performance Electronic Systems Containing Lead-free Solder." Such a plan will include reliability, configuration control, risks and limitations of use, and the effects of tin whiskers, plus the repair, rework, maintenance, and support of the equipment. However, the preparation of a standard or plan does not necessarily impose the use of lead-free electronics. Instead, it demonstrates an understanding of the impact of the component and materials supply situation in order to mitigate risks. Although the U.S. is likely to adopt similar legislation pertaining to RoHS in the near future - and despite possible exemptions for military and aerospace - some newer programs such as the Future Combat System (FCS) are already being selectively proactive in moving to lead free.

#### Lead-free solder

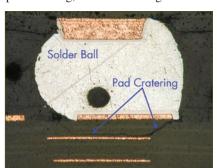

Using lead-free solder is the most obvious change, and it has a number of secondary effects on reliability. A leading contender for lead-free solder is SAC305 (Ag silver 3.0 percent, Cu - copper 0.5 percent, the remainder being Sn - tin). This type of solder has some undesirable mechanical characteristics compared to tin/lead:

- Its higher melting point exacerbates manufacturing and rework stresses in components and the Printing Wiring Board (PWB).

- Its microstructure is less homogeneous, causing its properties to be more orientation dependent.

- The absence of lead results in stiffer solder joints. During extended thermal cycling, this increased stiffness can become a critical reliability issue for larger Ball Grid Arrays (BGAs) due to stresses imposed by differential rates of expansion between the device and PWB.

The long-term solution does not lie with expedients such as interposers or replacing solder balls with tin/lead but instead lies in additional material research. New, more stable PWB materials have been developed to reduce some of these effects but in turn have introduced the risk of pads tearing from the PWB, known as pad cratering, illustrated in Figure 1.

Figure 1 | The cross-section photo shows pad cratering on a lead-free solder joint. Stiffer lead-free solders and more brittle PWB materials are leading to an increased risk of pad cratering on lead-free boards.

#### Tin whiskers

Tin whiskers is a phenomenon whereby thin conductive filaments grow from the

surface of a tin-plated termination that can potentially short-circuit adjacent pins of devices. The cause of whiskers is not entirely understood but is believed to be related to compressive stresses in the plating. It can happen at any time during the equipment's life and is therefore difficult to predict or mitigate. However, the most effective mitigations for tin whiskers include design rules that reduce the risk of shorts between solder pads, in addition to some types of conformal coatings that counter whisker growth.

#### Impact on COTS vendors

Suppliers of COTS embedded computing equipment are planning to introduce lead-free assemblies for military applications. But, as lead-free technology is introduced, it will require much additional test and qualification data to support its use in deployable projects. There will be a lengthy transition period during which COTS vendors will continue to manufacture and support both tin/lead and leadfree alternatives of the same product lines and provide the levels of configuration and materials management required to maintain each type of product over the life cycle. Curtiss-Wright Controls Embedded Computing (CWCEC) has adopted a proactive approach, having already amassed much test data, introduced new materials and test regimes such as Interconnect Stress Testing (IST), and developed the full manufacturing and life-cycle capability to introduce lead-free assemblies.

Lead-free products will require additional testing and tailoring during development to optimize long-term reliability, and COTS vendors will need to incorporate this data into their customers' projects lead-free plans. The rate of adoption of lead-free electronics for use in harsh environments will be determined partly by legislation but primarily by both vendors' and integrators' accumulated knowledge base and continuing research and development efforts.

To learn more, e-mail John at john.wemekamp@curtisswright.com.

### **Trapped in Your Design?**

## Break free with our space-saving solutions.

Escape the limitations of your board design with advanced microelectronics solutions from White Electronic Designs. Use our compact, high density memory modules to free up board space and improve performance.

Try our new DDR2 SDRAM that packs 1 GByte into a SnPb BGA package less than 1/2 in<sup>2</sup> ... or our new embedded SLC NAND flash BGA that has the performance of a solid state disk drive in a form factor that is one-fourth the volume of a comparable compact flash-based product.

WEDC lean microelectronic solutions are designed to solve component incompatibilities, reduce design complexity, and extend product life and environmental performance in military applications. We offer turnkey design, assembly and test of custom multi-chip solutions, and a wide range of standard military off-the-shelf space-saving solutions.

Expand the possibilities; change your perspective at www.whiteedc.com/escape.

602.437.1520 TEL | 602.437.9120 FAX

Outdated legacy code bases in warfare and defense systems create vulnerabilities to safety and prohibit the introduction of new, network-centric technology. With static analysis, these systems can be retrofitted to be high integrity, making devices more technologically competitive.

#### The need to modernize

The world of warfare and defense has changed. In the past 10 years alone, the main factor in ranking the best military has changed from merely possessing the largest and most powerful fighting force to having the best possible communication between personnel and military machines on the battlefield. These military machines are no longer as hardware-centric as they were decades ago; most employ embedded software systems to perform essential functions. The Abrams M1 tank currently deployed in Iraq and Afghanistan, for example, has a computer-aided targeting system that allows precise aiming in conjunction with a thermal imaging system.

These types of embedded systems are designed to be as robust and reliable as possible since lives depend on their effectiveness. These systems are highly specialized and - once built and deployed to the field - are generally meant to be used without further retrofitting for the lifetime of the unit. Unfortunately, such a design philosophy does not take into account the increasing roles these systems are required to perform eventually, as technology progresses, and safety can become an issue.

In the same way, increasingly, networking has taken on an expanded role in military devices over the past few decades. Modernizing legacy systems to take advantage of new networking functionalities, which rely on software, has become mandatory. Today, tanks and other vehicles are now nodes in a larger interconnected system that continually shares information. Each node in the system can work with other nodes in its network (or even nodes in other networks) to solve problems that could not be handled by any one system.

Software-driven systems like Mine-Resistant Ambush Protected (MRAP) vehicles containing Communication-On-The-Move (COTM) systems depend on software architecture and must be modernized to become network-centric,

for example. And modernization is a good strategy, even when optional, because doing so can reduce software maintenance costs in the long run. Once built, legacy applications should theoretically last forever, but they seldom do because routine maintenance ultimately causes the code base to deteriorate. Maintaining old code is very expensive (as high as 10 percent of the initial development budget per year) because it involves patching vulnerabilities and improving reliability. This is usually done by expensive developers possessing a rare right skill set. In contrast, new code is much cheaper. Although modernizing code has a higher price up front, it is often better to do so because regular long-term maintenance of legacy code costs more in the long run.

Legacy systems are generally modernized (but not fully replaced with new units due to cost) because many currently deployed military systems have at least another decade of planned functional lifetime left. Since safety and reliability are paramount, it is essential to modernize software to include the desired new capabilities without compromising previous quality or going over budget. Static analysis makes this task easier than it would be otherwise.

#### Static analysis for modernizing legacy code

Retrofitting legacy code for new functionality or to bring it up to new standards should not be done lightly. Since legacy systems are often mission critical and already deployed in the field, revisions should introduce minimal new coding defects into existing code. As a code base becomes more complicated, it becomes more difficult to isolate and eliminate defects since there are more variables that might interact with and stack on top of other defects in unforeseen ways.

While older tools use syntax and stylebased testing, modern static analysis uses path simulation through dataflow analysis in conjunction with Boolean satisfiability. Path simulation works by emulating what a program will do once it has been compiled and executes each function in its code base. This allows for the added detection of resource allocation issues, pointer mismanagement, improper buffer and string usage, and tainted data handling. Boolean satisfiability translates every operation in a program into Boolean variables and uses this data to test for potential runtime problems like integer overflows. These methods generate a false-positive rate as low as 15 percent.

To the rescue, however, is static analysis, which helps developers refactor and restructure the code bases of legacy programs to bring them up to modern standards. Static analysis reveals the steps performed at the creation of a legacy project so developers can understand the current architecture and original intention of the program. This feature innovation alleviates much of the guesswork of detecting resource allocation issues, pointer mismanagement, improper buffer, string usage, and tainted data handling when trying to upgrade code. Static analysis tools, such as those offered by Coverity, are also able to display information about any defect in question and show how it adversely affects the overall program.

Defense, similar to other software dependent industries, cannot afford to allow its technology to lag behind the times. The modernization of legacy code is inevitable, but advanced static analysis provides a sure remedy.

Tom Schultz brings 30 years' experience to his role as Director of Products at Coverity. Previously, Tom was founder and CTO of Codefast, which Coverity acquired in 2007. Tom also spent more than 10 years at Rational Software and later IBM Rational. He holds a B.S. in Biology-Geology from the University of Rochester. He can be contacted at tschultz@coverity.com.

### Daily Briefing: News Snippets

By Sharon Schnakenburg, Assistant Managing Editor

www.mil-embedded.com/dailybriefing

#### 'Background' technology moves forward in development

While the Orion Crew Exploration Vehicle (CEV) gets all the limelight for its part of NASA's year 2020 moon-and-beyond Constellation Program, the Orion CEV wouldn't get off the ground, literally, without its more "background" technology: the perhaps less-glamorous (but just as essential) 25-ton payload capacity Ares 1 vehicle booster (Figure 1). Consequently, Ares 1 development is progressing with a recent contract between Ball Aerospace & Technologies Corp. and Aitech Defense Systems. The contract specifies that Aitech provides its S950 single board computer, in addition to its S750 PMC, to be utilized for Ares 1's Command Telemetry Computer (CTC) and Instrument Unit Avionics (IUA) Flight Computer (FC) systems. CTC and IUA FC systems proffer the navigation, control, and guidance hardware for Ares 1 and act as a vehicle control subsystem when the rocket ascends into orbit. The S950 will lend its 1 GHz processing capability, while S750 will render high-speed data imaging to Orion CEV's ground support system and solid-state recorder.

Figure 1 | Ares 1 photo courtesy of Aitech

#### **Turkish Armed Forces build SCA** repertoire

Prototyping ... porting ... testing ... it's all in a day's work when developing SDR waveforms. Thus, Spectrum Signal Processing by Vecima's ("Spectrum's") flexComm SDR-4000 multipurpose, SCA-compliant transceiver will be used by The Scientific and Technological Research Council of Turkey (TUBITAK) and the National Research Institute of Electronics and Cryptology (UEKAE) for the aforestated triad of purposes. Specifically, "TUBITAK UAKAE" will use flexComm SDR-4000 within the final phase of its twofold SDR project: Building a test bed for testing and developing SCA-compliant waveforms per Turkish Armed Forces (TAF) specifications, and SCA verification and testing on SDRs to be utilized by the TAF.

#### Helmet jettison device to enlighten

Sometimes the full ramifications of events are not understood until much later, if at all. However, the U.S. Air Force is aiming to change that with a recent Small Business Innovation Research (SBIR) Phase 1 grant to Diversified Technical Systems, Inc. (DTS) for a helmet jettison device. The project's threefold objective is to design a helmet-mounted device that can execute real-time analysis of sensor data; to create simulated eject conditions under which the device is tested; and to perform analysis on existing testing data on ejection events and Air Combat Maneuver (ACM) events. Based on a customized version of DTS's e-SENSING Embedded Recorder (ER), the smart helmetmounted sensor system will specifically be used in the measurement and detection of blunt impact and blast events and will send a release signal to the Helmet-Mounted Display System (HMDS) during eject events.

#### Iraqi Air Force's vision widens, courtesy of USAF

Situational awareness makes or breaks a mission – and the safety of military personnel and nearby civilians. Consequently, the USAF and Lockheed Martin recently penned a \$28.1 million Phase 1 contract to enhance the situational awareness of the Iraqi Air Force in the civilian and military airspace. The Iraq Air Command and Control System contract, awarded by Hanscom Air Force Base's Electronic Systems Center in Massachusetts, is designed to afford the Iraqi Air Force with modernized C2 technology interoperable with Coalition forces. Specifically, the agreement stipulates that Lockheed Martin renders the Iraqi Air Force an integrated technology network comprising: a Groundto-Air Transmitter and Receiver (GATR) site, a networked comms infrastructure consisting of a training suite and Sector Operation Center (SOC), and a long-range AN/TPS-77 radar system (Figure 2) for air surveillance. Delivery is slated to occur inside the next 27 months.

Figure 2 | AN/TPS-77 radar system, photo courtesy of Lockheed Martin

#### 3U VPX drafted for M1A2

The 3U VPX (VITA 46) form factor will soon be tucked inside the U.S. Army's rough-and-ready Abrams M1A2 tank (Figure 3), according to a recent contract between prime General Dynamics Land Systems (GDLS) and GE Fanuc Intelligent Platforms. As part of the Army's M1A2 Abrams Evolutionary Design (AED) program, GE will supply 3U VPX wares including: graphics processors, single board computers, switches, and disk subsystems. The bonus capability: The wares are all additionally incarnated in accordance with the REDI (VITA 48) specification, yielding resiliency in the harshest environments and easing Two Level Maintenance via their Line Replaceable Module (LRM) format. Specified under the contract are GE's SBC340, an SBC based on the Intel Core 2 Duo processor; SBC310, a Freescale 8641D-based SBC; SDD910 solid-state SATA disk module; GBX410 GbE switch featuring 16 ports; PEX430 PMC/XMC carrier and PCI Express switch; and the GRA110 NVIDIA G73 graphics processor. AED will gradually supersede the current GE Fanuc-supplied 6U VME-based systems under the Abrams Continuous Electronics Enhancement Program (CEEP) and System Enhancement Program (SEP V2).

Figure 3 | M1A2 Abrams tank, U.S. Army photo

#### PHM extends 'advanced aircraft' life cycles

Though it has, of course, been targeting matters of national security for decades, the U.S. Air Force has a relatively new target: the identification and analysis of jet engine equipment degradation. Accordingly, the USAF recently awarded DSPCon, Inc. a Phase II Small Business Innovation Research (SBIR) contract for ongoing optimized-processing-platform development, in accordance with the USAF's goal of heightening Propulsion Health Management (PHM) systems' signal processing capabilities. As the platform in development provides real-time data capture and enhanced diagnostics, the USAF can detect jet engine equipment degradation faster and more thoroughly, before equipment fails. The net result: Extended and improved equipment life cycles. PHM technology will be utilized in "advanced aircraft" and commercial aircraft applications.

For consideration in Daily Briefings, submit your press releases at http://submit.opensystemsmedia.com. Submission does not guarantee inclusion.

Figure 4 | AH-64 Apache, U.S. Army photo by Sgt. 1st Class Brent Hunt

#### **Boeing demo embodies Future Force**

The U.S. Army knows that networking technology such as its Wideband Networking Waveform (WNW) can bring to life its vision of Future Force networking, enabling video, voice, and data communications between military personnel in the sky and on Earth. Accordingly, Boeing recently held its first WNW integrated capabilities demonstration. Held at the U.S. Army's C4ISR On-The-Move (OTM) Event 09, the demonstration comprised an airborne AH-64 Apache helicopter (Figure 4), a tactical operations center, several High Mobility Multipurpose Wheeled Vehicles, and an airship, all equipped with surrogate JTRS radios sporting WNW version 3.1a. The WNW network was monitored by a Boeing-designed network management software that proved compatible with the network operation manager system of Warfighter Information Network-Tactical (WIN-T). Demonstration information transmitted by WNW consisted of imagery, streaming video, spot reports on hypothetical enemy forces, and more.

#### **USMC radios: Making the grade?**

Whether in legacy or new digital style, U.S. Marine Corps' radios need testing to keep them at "grade A" level. Thus, the USMC recently granted Aeroflex a \$40.5 million, five-year contract for Ground Radio Maintenance Automatic Test Systems (GRMATS): Aeroflex's 7200 Configurable Automated Test Set (CATS). The 7200 CATS (Figure 5) is designed to test SDRs such as military tactical radios, with a modular design to easily accommodate future technology. The 7200 CATS is also crafted for compatibility with the Joint Tactical Radio System's (JTRS's) Software Communications Architecture (SCA) and includes multi-gbps data buses featuring plug-and-play software architecture. Additional highlights include MIL-PRF-28800F Class 3 packaging, 90 MHz signal generation and instantaneous digitization bandwidth, 2.6 GHz frequency coverage, and phase noise capability of more than -108 dBc/Hz.

Figure 5 | 7200 CATS test system, photo courtesy of Aeroflex

#### 'EAL 6+' says it all — or does it?

#### Q&A with Marc Brown, Vice President, VxWorks Product Strategy and Marketing for Wind River Systems

#### **EDITOR'S NOTE**

To be or not to be ... EAL 6+ certified: That is the question. Apologies to William Shakespeare, but you get the point. With EAL 6 (or 6+) certification becoming the latest trend among embedded software vendors, the criteria for achieving such should be fairly straightforward ... or is it? Marc Brown, VP over VxWorks Product Strategy and Marketing at Wind River Systems, reveals what he claims are misassumptions about EAL 6+, as the company's VxWorks MILS Platform 2.0 undergoes NSA/NIAP evaluation for EAL 6+ compliance. He also has a thing or two to say about the company's recent acquision by Intel, multicore, and a clarified focus for the future. Edited excerpts follow.

MIL EMBEDDED: Wind River recently announced its VxWorks MILS Platform 2.0, which is now listed on the NSA-operated National Information Assurance Partnership's (NIAP's) website<sup>1</sup> as "In Evaluation" for compliance to High Robustness and Common Criteria Evaluation Assurance Level (EAL) 6+. What was the impetus?

be two or three computers, each based on different security levels and the actual hardware line that they plug into.

VxWorks MILS provides a development environment that allows systems with multiple levels of security to be collapsed into a single system, and the operating system itself provides the data separation ation. We've really tried to take a different approach from some other companies in that we've developed the MILS separation kernel from the ground up to be compliant with the U.S. government protection profile for separation kernels<sup>2</sup>. We're not tweaking or trying to force any new requirements into an existing product.

BROWN: We've got a pretty long history with products that have been safety-certified. And there are quite a few people using VxWorks 653 as well as our certified VxWorks products for safety-critical applications such

as avionics. VxWorks MILS Platform 2.0, though, is really our first widely available platform for highly secure environments. It's designed for cases where there are different levels of data, whether it's data at different classification levels - maybe unclassified, classified, secret, or top secret – or data from coalition partners, for example, and these need to coexist securely on the same hardware system. There are many more applications these days that have security requirements on how to handle that data. Unfortunately, for many organizations today, the only way they know how to deal with different levels of security is to use redundant hardware or systems. Instead of having one computer on your desk, there might

... There are two or three requirements that actually need to be added into the "high robustness" definition to fulfill the requirements of EAL 6.

required to deal with these multiple levels of security or data classification. This reduces the costs for our military: For example, soldiers on the battlefield might need to carry two or three mobile handheld radios, each handling communications at different security levels, but now they can use one single radio that provides the same secure communication services. Separation is becoming a mandatory requirement these days.

MIL EMBEDDED: How have NSA and NIAP played into VxWorks MILS 2.0's development?

BROWN: We're working very closely with NSA and NIAP, certainly, to do our evalu-

We're working closely with NSA and the University of Idaho on the formal methods evaluation. The end goal is that once someone buys this particular environment, if they need to change the hardware, a re-evaluation will be as cost-effective

as possible in that they won't have to recertify the entire system. They'll be able to reuse certification artifacts for the majority of the system, and only need to re-evaluate the lowest layers of software that have been affected by the change in hardware.

MIL EMBEDDED: Tell me a little more about VxWorks MILS 2.0 itself.

BROWN: VxWorks MILS 2.0 provides a Separation Kernel (SK) as well as a number of other key capabilities, but I won't go through all of them now. VxWorks MILS 2.0 is really focused on providing key SK capabilities, interpartition communication capabilities, and networking

<sup>&</sup>lt;sup>1</sup> NIAP's listing of validated products can be found at: www.niap-ccevs.org/cc-scheme/vpl

<sup>&</sup>lt;sup>2</sup> NIAP's certification documentation can be found (and subsequently downloaded) from: www.niap-ccevs.org/cc-scheme/st/vid10119

capabilities. This release supports the Power Architecture. Other architectures will be supported in the near future.

MIL EMBEDDED: What's the significance of the SK technology in VxWorks MILS 2.0?

BROWN: I think one thing of significance to note with VxWorks MILS 2.0, at least from a technical perspective, is that VxWorks MILS 2.0 was built using a Type 1 hypervisor technology. There are two approaches: You can either go with a Type 2 hypervisor, which basically utilizes an operating system to act as a hypervisor. Or you can use a Type 1 hypervisor that's a separate technology that's very lightweight, very small, and provides the fundamental services. In this case, it provides the services necessary to be compliant with the Separation Kernel Protection Profile (SKPP), suitable for EAL 6+ certification levels, but provides for better system performance than a Type 2 hypervisor-based system. Our VxWorks 653 platform uses Type 1 hypervisor-based virtualization to achieve very high performance, even with dozens of user-mode partitions.

In addition, we have the VxWorks guest operating system that can be utilized in the partitions, really giving VxWorks users great API compatibility so they can take their applications and plug them into a MILS environment. And at that point, they've got these applications that they can now reuse in a fully secure environment.

MIL EMBEDDED: When you say a Type 1 hypervisor is "very small," how many lines of code are we talking about?

BROWN: I don't think we've released the number of lines of code, but it is definitely in the lower thousands of lines of code.

MIL EMBEDDED: What role does the SKPP play in EAL 6+ certification?

**BROWN**: The SKPP provides guidelines for developing a separation kernel, which is what actually goes through certification. We have a developed a separation kernel based on the NSA-approved SKPP that will go through the EAL 6+/high robustness certification.

MIL EMBEDDED: How is this different or similar to how Green Hills got its INTEGRITY-178 RTOS certified?

BROWN: It's different. Green Hills took a Type 2 hypervisor approach. And they only certified under "high robustness"; they did not certify under EAL 6+, as they did not actually add in the necessary requirements to comply with EAL 6. We're actually taking a very similar Type 1 hypervisor-based approach as LynuxWorks, but we think it's important for us to be certified under both the common criteria EAL 6 and also under "high robustness."

MIL EMBEDDED: You're telling me certification to EAL 6+ is different from being certified and categorized as "high robustness." Those two terms are not analogous<sup>3</sup>?

BROWN: That's correct. They're very similar, but there are two or three requirements that actually need to be added into the "high robustness" definition to fulfill the requirements of EAL 6. One of the reasons Green Hills is not listed on NIAP's website under systems evaluated at EAL 6+ is that there are certain requirements that have to be satisfied in addition to developing in compliance to the SKPP.

MIL EMBEDDED: When will VxWorks MILS 2.0 be certified?

BROWN: Our current plan is for certification to be accomplished by the end of 2011.

MIL EMBEDDED: Wind River's ARINC 653 partitioned OS is a completely different kernel from the one we're talking about now, correct?

BROWN: Yes, exactly. They're both based on virtualization technologies, but VxWorks MILS 2.0 was designed to comply with the guidelines in the SKPP to achieve certification to EAL 6+ and "high robustness."

The CONEC embedded connector series covers the wide range of specified connectors used in todays embedded computing applications:

- MicroTCA

- AdvancedTCA

- CompactPCI

- PC/104 and PC/104plus

- DIN 60603-2 Eurostyle

**TECHNOLOGY IN CONNECTORS**

Garner, NC. 27529 Tel. + 1 919 460 8800 Fax +1 919 460 0141 E-mail info@conec.com www.conec.com

**CONEC** connector products are available at DIGI KEY INC. and MOUSER ELECTRONICS

<sup>&</sup>lt;sup>3</sup> An interview with Green Hills CTO Dave Kleidermacher can be found at: www.vmecritical.com/articles/id/?3747

MIL EMBEDDED: By now everyone knows about Intel's recent acquisition of Wind River. Can you make any comments in respect to what we've talked about?

BROWN: There's intent for Wind River to maintain its independence and continue driving forward with its defined plans. I think we've got some really strong roadmaps and strategies laid out – for various architectures such as Intel, PowerPC, ARM, and MIPS - that span the next 18 months to 3 years that we're going to continue to drive forward.

MIL EMBEDDED: About five years ago, we were hearing lots of awful things about the platform strategy that Wind River had launched, which was confusing a lot of people. There was a transition out of Tornado. There was also the "Hell no, we'll never do Linux," then "Guess what - now we're doing Linux." But I think Wind River is well sorted at this point in time. Where is your focus now?

BROWN: We've clarified our focus much more. It's great because we've got broad coverage across many vertical markets. And then some of the new technology disruptions, especially multicore, have been really good for Wind River in that they have allowed us to apply a lot of the technological history that our company's built up. It's amazing to me when I hear about processors in the works with hundreds of cores versus the dualor quad-core processors that people are already struggling with. I think customers will need operating systems that can somewhat shield them from the complexity of the processor while also being optimized. That's a big area that we're highly focused on.

#### MIL EMBEDDED: With FPGA

companies focusing on interfacing with lots of different cores, might it seem natural to Wind River that operating systems like VxWorks are going to have to find their way a lot more formally into FPGA-based and multicore designs?

BROWN: Yes, definitely. It's been amazing for us to watch some of the new processors coming to market with dedicated acceleration engines - built into a multicore design - that are very vertical market-centric. They're certainly useful in the networking and wireless markets, and we have heard that the industry is going to see more and more multicore chips with FPGAs. If there's an FPGA on the silicon, you can basically tailor that chip for any particular vertical market. So it's only natural that an operating system such as VxWorks or Linux actually will be able to support that.

Marc Brown is Vice President, VxWorks Product Strategy and Marketing for Wind River Systems. He has more than 18 years of experience in the development and deployment of highly technical missioncritical systems. He also served as VP of Product Marketing and Strategy for Borland Software and held senior management positions at IBM and Rational and technical positions at Motorola and Corning. He can be contacted at marc.brown@windriver.com.

> **Wind River** 510-749-2238 www.windriver.com

### » We Do Not Build Navy Ships «

#### Our Customers Do.

At the heart of the most advanced command and control systems deployed in Navy ships are Kontron Military Rugged COTS boards and systems. Keeping us safe with smart applications, military contractors look to Kontron for superior technology, performance and life cycle management expertise.

#### MILITARY RUGGED COTS

Call, Email or Visit today.

Call: 1-888-294-4558

Email: info@us.kontron.com

Visit: www.kontron.com/military

#### Hardware: Mil apps blend real-time with realism

10 GbE provides a standards-based "fat pipe" to move data. However, real-time applications present unique challenges that must be addressed at the outset.

The world of technology has flipped 180 degrees: No longer is the best technology developed for the military and then later commercialized. Now, the defense department is playing catch-up to off-the-shelf technology. These days, civilians are accustomed to a profoundly high level of networking connectivity, enabled largely by Ethernet and Internet Protocol (IP). The military wants the same.

The appeal of Ethernet-based networking in the digitized battle-field is clear. And with the advent of 10 GbE, Ethernet is no longer limited to the command and control fabric in systems. It can also function as a "fat pipe" that reaches all the way down to high-bandwidth sensors. So, it's not surprising that 10 GbE is being designed into more and more defense applications, both in the main network and as the pipe to and from sensors or effectors.

But using 10 GbE is not without problems.

#### The fire hose crisis

Ever try to drink from a fire hose? It's not a matter of digesting or processing the water. You can't even ingest it. A processor faced with a 10 GbE pipe has the same problem.

It takes about 1 GHz of CPU processing per Gb of Ethernet traffic. CPUs fall quite short of bandwidth trying to run Ethernet protocol at 10 Gbps.

This problem also applies to commercial servers, but adopting commercial-world solutions for net-centric defense applications doesn't work. Let's look at why commercial network cards don't fit the bill.

#### The problem of handling bursts

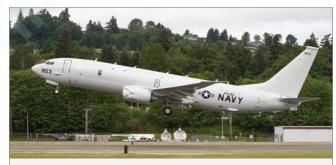

High-performance real-time sensor applications, such as ELINT analysis systems found on platforms like Boeing's P-8A Poseidon (Figure 1), often need to sample in high-speed (hundreds of MSps) bursts lasting at least a few milliseconds. For a single channel, this leads to an incoming large data blast of at least 10 MB to 30 MB. On a 10 GbE link, this corresponds to receiving 1,000 to 20,000 back-to-back packets at line rate (depending on the MTU size employed).

Figure 1 I High-performance real-time sensor applications, such as ELINT analysis systems found on platforms like Boeing's P-8A Poseidon (pictured), often need to sample in high-speed (hundreds of MSps) bursts lasting a few milliseconds. Boeing photo by Ed Turner

If the receiving interface cannot absorb all this data into system memory, data is dropped. In a commercial server environment, dropped packets are resent. But in sensor applications, there is no time and/or no hardware facility to resend the data. Typical commercial 10 GbE interface cards, designed and cost-optimized for an environment where re-transmission of data is permitted and line rate bursts are rare, simply cannot address this problem.

#### Beyond protocol offload

In many real-time applications, offloading the transport protocol provides only part of the solution. For instance, COMINT or ELINT direction finding, network surveillance, and intercept are examples of applications that collect sensor data to synthesize multidimensional models of the environment. Such applications rely on the fusion of the sensor data. Bringing the data together requires accurate and precise time stamping of the individual data streams. Outgoing data in Electronic Countermeasures (ECM) or simulation systems must similarly be precisely time gated and synchronized to other events.

Precise time stamping and gating can only be performed through a deterministic interface. The CPU, vulnerable to software interrupt latencies and inconsistent access to buses, cannot provide the necessary time-stamp precision. Similarly, commercial Ethernet cards, with or without offload, get traffic from place to place. Time stamping is typically not a part of their functionality.

Time stamping is an example of additional special functionality required by these real-time applications. Another kind of problem occurs when offloading the protocol still results in data rates that are too high to be managed after they leave the interface. Take a multicamera GigE Vision-based situational awareness system that runs on top of standard UDP protocol or an intrusion prevention system guarding a network from viruses, Trojans, and other cyber threats coming from the WAN where the contents of packets are inspected at line rate. Both applications execute on payload data arriving at a 10 Gbps rate. So, offloading only the transport protocol, as a commercial offload solution would do, still leaves the CPU struggling to process data at 10 Gbps.

#### Making a mountain out of a molehill

Real-time digitized signals are destined for signal processing such as low or band pass filtering or error correction. These algorithms correct or compensate for small runs of errors, such as the error in a few consecutive data points. When faced with a large run of consecutive errors (such as when a large group of samples is missing), the algorithms break down.

This is particularly relevant for Ethernet data that transmits in packets with checksums and Cyclic Redundancy Check (CRC) fields that check for errors in the packets. Per the protocol standard, when errors are detected, even if they were caused by an error in a single data point, the entire packet is discarded. This means that as many as 9,000 consecutive bytes go missing, subsequently choking the signal-processing algorithm (Figure 2). If those few errors had instead been delivered to the signal-processing algorithm, they would not have caused a problem. So, the standard protocol stack behavior can make a mountain out of a molehill in a real-time signal processing system.

#### The real-time 10 GbE alternative

These problems can be circumvented with an intelligent 10 GbE interface. FPGA-based solutions are capable of the line-rate performance and flexible enough to run algorithms optimized for application requirements. Unlike CPUs with their sequential manipulation paradigms, data flowing into an FPGA cascades like

## Mountain from a Molehill 1,3,5,7,9,11,13,15,17,19,17,16,14,12,10,8,6,4,2,1,3,5,7,9,... 1,3,5,7,9,11,13,15,17,10,20,16,14,12,10,8,6,4,2,1,3,5,7,9,... Signal Processing Algorithm 1,3,5,7,9,11,13,15,17, 1,3,5,7,9,11,13,15,17, Algorithm Algorithm

- Small error causes checksum mismatch and packet drop

- Packet drop: lose 1.5K to 9K consecutive bytes

- · Algorithm chokes

- If had passed the small error to signal processing in first place, it would have been a non-issue

Figure 2 | When errors are detected, the entire packet is discarded, resulting in as many as 9,000 consecutive bytes going missing and subsequently choking the signal-processing algorithm.

a waterfall over massive amounts of parallel configured logic. In today's large FPGAs, the data flows over pipelines of hundreds of thousands of logic cells that can effectively be running at a few hundred megahertz. For the I/O, modern FPGAs are equipped with high-speed transceivers running at up to 11 Gbps. This allows them to interface to high-speed serializers or directly into the high-speed optical or copper communications interfaces. Using clever designs, even modern medium-sized FPGAs – containing, say, a hundred thousand cells – can fit multiple channels of real-time 10 GbE interfaces along with higher-layer application functionality.

A real-time 10 GbE system should include:

- Sufficient memory to accommodate the extended duration, line-rate bursts

- A time stamp and synchronization interface to deterministically and precisely stamp packets entering or exiting

These systems should additionally comprise algorithms optimized for real-time requirements that might include:

- A transport layer protocol offload tailored to the application, bus interface, and processor

- A process that alleviates CPU burden by offloading intensive application processing operations or inspecting and dropping packets that are uninteresting before they ever get to the CPU

Modifying the standard transport protocol behavior to tag but not drop the packets received with checksum errors

No question, civilian COTS technologies – from the ubiquitous Internet to the gaming console in your living room – are finding their way into the digitized battlefield and changing both expectations and the nature and capabilities of net-centric warfare.

When it comes to using 10 GbE in these high-performance real-time applications, it is not enough to simply grab the mass-market technologies off the shelf. Instead, while understanding and respecting the unique requirements of net-centric warfare applications, we need to tailor the implementation of the standardized 10 GbE interface to meet these real-time needs.

Rob Kraft is VP of Marketing at AdvancedIO Systems Inc. He has more than 13 years of experience in systems engineering and business roles in the embedded real-time computing industry. Prior to joining AdvancedIO, he worked at Spectrum Signal Processing and AlliedSignal Aerospace. Rob has an MASc in Electrical

Engineering from the University of Toronto. He can be contacted at RKraft@advancedio.com.

AdvancedIO Systems Inc. 604-331-1600 • www.advancedio.com

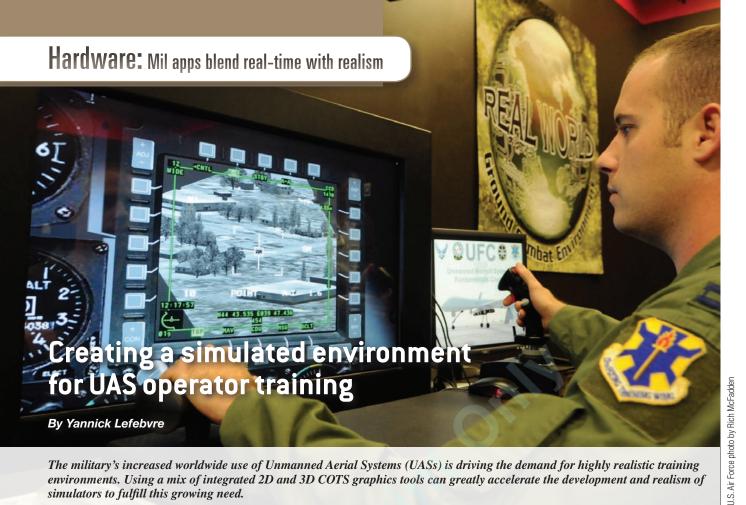

The military's increased worldwide use of Unmanned Aerial Systems (UASs) is driving the demand for highly realistic training environments. Using a mix of integrated 2D and 3D COTS graphics tools can greatly accelerate the development and realism of simulators to fulfill this growing need.

Unmanned Aerial Systems (UASs) are increasingly being used by military forces around the world. Whether for reconnaissance work or tactical engagements, unmanned vehicles are remotely controlled from a ground station and provide extraordinary capabilities in range and agility while eliminating risk to human life. To execute tasks, operators need to be trained in a variety of skills, from the interpretation of visual information that the UAS provides to reacting correctly based on the situation at hand.

Simulating a UAS ground station is complex and requires many different technologies to work together to produce the final result for trainees. When creating a simulated environment for operator training, critical elements such as the UAS's sensor output and graphical overlays that display data used to pilot or control the vehicle need to be delivered in an intuitive way to ensure an effective training environment is provided.

From a system design perspective, it may be easier to simulate sensor outputs and graphical overlays on several different screens using disparate technologies. From a trainee's perspective, this approach can create unnecessary

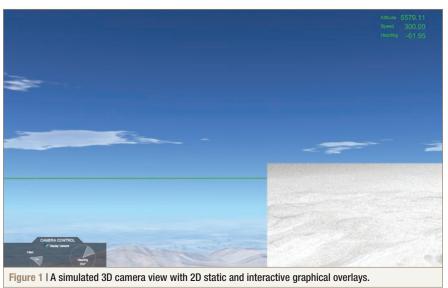

workload and the significance of an overlay's exact positioning over the UAS's sensor feed could be lost. The optimal solution is to merge both the UASs sensor feed and its visual overlays into a single screen using a Commercial Off-the-Shelf (COTS) 3D image generator with a COTS 2D human-machine interface modeling tool to ease the process of merging these applications and provide a more effective and intuitive UAS training system (Figure 1).

#### Matching requirements with technology

COTS 3D image generation systems are available to simulate UAS sensor feeds. This type of application can render synthetic animated environments onscreen such as terrain, buildings, moving vehicles, atmospheric effects, and any other details that make a virtual world come to life. Beyond receiving continual product updates over the lifespan of a project and benefiting from a proven framework,

Hardware: Mil apps blend real-time with realism

opting for a COTS image generator brings additional functionality that elevates the realism of a UAS ground station simulator such as simulating high-fidelity sensors (night vision goggles and infrared, for example). In contrast, developing such advanced visual features in-house is cost-prohibitive, time-consuming, and quite challenging as it requires a very specific expertise.

For the 2D overlays that are presented to the operators on top of the sensor feed, such as a Heads-Up Display (HUD) or a targeting reticule, a COTS Human-Machine-Interface (HMI) design software is best suited as it enables developers to visually define the elements of the overlay along with their respective functionality, data ranges, and information sources without needing to write code manually. Once a design is finalized, an automatic code generator packages the display contents as a self-contained executable program. Using a COTS HMI design software for this part of the development introduces advanced authoring concepts such as graphical logic creation and accelerates the development cycle by using a graphical user interface instead of manual coding.

#### Integrating 2D and 3D graphics

Once the 2D overlays and 3D graphics have been developed, they need to be integrated into one cohesive method to provide the trainee an integrated view that accurately represents the real-life equipment.

For this to be possible, both the 2D HMI design software and the 3D image generator need to use the same graphical language to draw graphics on-screen. If they don't, it will be difficult – if not impossible - to integrate them within the same environment. In today's desktop and embedded computing world, the graphical language of choice is usually OpenGL.

Another concern that needs addressing is that the graphics code produced by the HMI design software needs to adapt itself to being rendered in a larger environment and not clear the screen buffer when it renders its graphics so that the underlying 3D graphics don't get erased.

One last consideration before starting the integration of these two technologies is

... Opting for a COTS image generator brings additional functionality that elevates the realism of a **UAS** ground station simulator such as simulating highfidelity sensors ...

the authoring of the 2D overlay graphics. Since they will be rendered on top of the 3D environment with transparent elements, graphical techniques such as masking (using visual elements that are the same color as the background as masks) should be avoided as they would produce undesirable visual artifacts.

There are two common approaches that can be followed to perform this integration. The first and more manual method is to take the generated code from the HMI design tool and call it from a post-draw function within the 3D image generator. A post-draw function is a programming hook that allows users to render their own graphics once the 3D virtual world has been completely displayed. This integration technique requires skilled programmers who are familiar with both technologies at hand.

An easier approach that is provided through the use of COTS HMI design software is to encapsulate the 2D graphical overlay as a Dynamic Link Library (DLL) plug-in with a defined communications interface and to load the resulting component in a COTS 3D environment that supports external plug-ins and offers a visual configuration utility. In addition to simplifying the integration of the visual overlays with the UAS sensor feed simulation, this technique makes it easy to iterate through the development of an application by only having to generate a new plug-in file after making changes to the overlay graphics.

Once the display code is loaded in the 3D display, it needs to be animated. Most often, this is done by sending data to the 2D overlay using a communications structure that is defined in the HMI design. Once data is assigned to the interface, the display elements that are linked to incoming variables automatically update

themselves to reflect new values. Figure 2 depicts the 3D rendering pipeline with 2D overlay integration.

RENDER

Render scene contents with all environmental and lighting effects

SENSOR

Apply post-processing effects to scene to simulate UAS sensor systems

POST-DRAW OVERLAY

Render 2D overlay graphics on top of 3D scene

In terms of data transport mechanisms, information can be sent by using API functions defined in the DLL plug-in or through direct communication between the overlay code and external data sources. The first method would be used if data displayed by the overlay is shared with the 3D scene (for example, pitch, roll, and altitude). The second technique is used in situations where the overlay data is hosted outside the visual system (for example, targeting reticule or engine data) and needs to be transported over protocols such as UDP, TCP, or shared memory.

Figure 2 | 3D rendering pipeline with 2D overlay

integration.

#### The benefits of an integrated solution

The use and integration of COTS 2D and 3D graphics is the best way to create an environment that is closest to the real equipment that trainees need to become familiar with in a UAS ground control station. The need for dynamic, intuitive and realistic training environments continues to increase in tandem with the growth of the UAS market. Developers play a key role in the creation of accurate and immersive training programs and must understand how COTS technologies such as HMI design software and a 3D image generating system help them deliver high-quality simulators efficiently. By eliminating the need for hand-coding

and using tools that offer advanced logic authoring and the ability to easily integrate 2D and 3D, developers will stay one step ahead of the market curve.

Yannick Lefebvre is a senior application developer at Presagis. With a background in computer sciences and 12 years of experience in modeling and simulation, Yannick has provided counsel on hundreds of simulation and embedded display programs globally and is considered an expert in the industry. He can be reached at yannick.lefebvre@presagis.com.

Presagis 514-341-3874 www.presagis.com

Publish-subscribe middleware is the key technology that enables data-centric architecture. The DDS standard precisely defines how the middleware controls and transmits information. Successful applications include many shipboard and UAV systems.

Modern networked applications must connect and coordinate many resources. A typical distributed application integrates CPU-intensive servers, data stores, user interfaces, and real-time sensors and actuators. Each of these applications demands a different set of information, at varying rates, with varying urgency, and with varying reliability.

Getting the right data to the right place at the right time in this complex environment is perhaps the greatest integration challenge of the new networked reality. The "traditional" way to connect these disparate systems is to first examine the data requirements of each device or processing endpoint, and then design point-to-point interfaces between those devices. Once the relationship has been established, the data can be passed between those two devices, likely using direct messaging. If many devices need the same information, a client-server design allows distributed access.

However, this design assumes the network is relatively static, servers are always present and accessible, the server/ client relationships are clear, clients know where and - most importantly - when to request data, and all nodes have similar delivery requirements. This "servercentric" design quickly breaks down as complexity grows.

Data-centric design offers an alternative. With data-centric design, developers specify only the data requirements, inputs, and outputs of each subsystem. Integration middleware discovers the producers and consumers of information and provides the data immediately when needed. This design greatly simplifies integration of systems with complex data requirements. Driven by the rapid adoption of the Object Management Group (OMG) Data Distribution Service (DDS) standard[1], many fielded systems including shipboard systems like Aegis, UAVs like Scan Eagle, and base stations like the Advanced Ground Control Station for Predator – are adopting this DDS and data-centric design, empowered by publish-subscribe middleware.

#### **Data-centric design**

Instead of focusing on endpoint applications (devices, processing nodes, console applications) and how they individually interact, the data-centric approach begins the design process from an information perspective. What data does this application produce? What does it need? When? These questions decouple the implementation of the application from the other parts of the system. Data-centric design can greatly simplify system concepts.

Thus, a data-centric designer first defines an information model that captures the essential state and events in the system, then creates data input and output specifications, and then develops components that can produce and process that information. Rather than deriving specific

data-interface requirements between components, the designer determines how to represent the state of the system and the external or internal events that can affect it. This "data model" captures the essential elements of the physical system as well as the processing logic. The model decouples applications; data can be provided by any (authorized) process and used by any other process. Applications must specify when and how they can supply information, but they do not need to know when or where that data might be used.

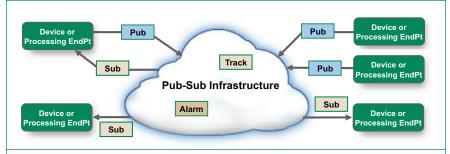

The enabling technology for data-centric design is publish-subscribe messaging, often shortened to "pub-sub." In this model, data sources, or producers, publish data into and subscribe to data from an "information bus" or "cloud" (Figure 1). Note that although there is a concept of data "in the cloud," it is a virtual concept. The actual data exists only in the publisher and subscriber endpoints. The pub-sub system connects endpoints by sending messages from the publishers to subscribers over a variety of transports, including direct-memory transfers, switched fabrics, or multicast or unicast over Ethernet. Transports, operating systems, and other location details do not need to be known, decoupling the design and allowing adaptation to performance, scalability, and fault-tolerance requirements.[2]

On a ship, for example, a GPS receiver can publish position data. Navigation computers and targeting systems can all

Figure 1 | Data-centric design revolves around the information itself. The information model captures the essential state and events in the system. Components are then built to interact with the information model "cloud," rather than with each other directly. The pub-sub infrastructure connects all the pieces.

subscribe to the GPS location data. The publications go directly from the GPS to the targeting system, even though both conceptually simply publish or subscribe to the "cloud."

By converting data within the middleware, publish-subscribe models can also connect systems with unmatched data formats. By enforcing quality of service parameters such as timing specifications and buffering, pub-sub models can connect systems with disparate delivery requirements, even trading off delivery reliability with timing constraints.

But the most important advantage of the publish-subscribe approach is decoupling. Since only the data interactions are specified, devices can be upgraded or added without the need to change code and exhaustively retest every configuration. If new data is available on the network, other devices might require additional code to make use of that data, but in practice this is significantly simpler than modifying and testing a large number of specific point-to-point connections.

Decoupling also makes distributed applications highly scalable. Because there are no fragile point-to-point data connections and devices can be added with little or no change to underlying code, expanding the application to include a larger network with more endpoints is simplified.

#### Designing with data-centric principles

Data-centricity provides a guide for how to design distributed applications in general. Many system architects of distributed applications today use procedural or object-oriented principles in creating the fundamental design, often using UML sequence, class, and state diagrams.

These design methodologies tend to treat transporting and consuming data as second-class citizens, focusing instead on the step-by-step processes by which devices make computations and produce actionable results. A data-oriented methodology, on the other hand, focuses on the flow of data through the application. In general, the tenets of data-oriented programming include the following principles:

- Expose the data. Ensure that the data is visible throughout the entire system. Hiding the data makes it difficult for new processing endpoints to identify data needs and gain access to that data.

- Hide the code. Conversely, there is no reason for any of the computational endpoints to be cognizant of one another's code. By abstracting the code, data is free to be used by any process, no matter where it was generated. This allows for data sharing across the distributed application

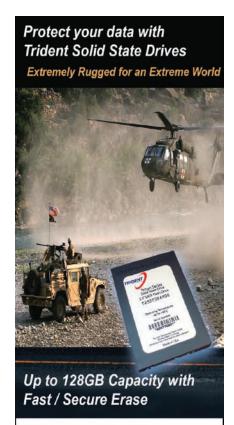

#### **Military Grade Solid State Drives:**

- Fast / Secure Erase for complete media de-classification

- · Purpose built for military applications utilizing Industrial Grade SLC NAND Flash (-40 to 85°C)

- ·Standard 2.5" Form Factor with anodized aluminum case

- ·Standard IDE or SATA interface with sustained speeds up to 100MB/s